“반도체 설계, AI가 하루 만에 끝낸다”…설계 패러다임 전환 신호 https://t.co/ReVipuuDro

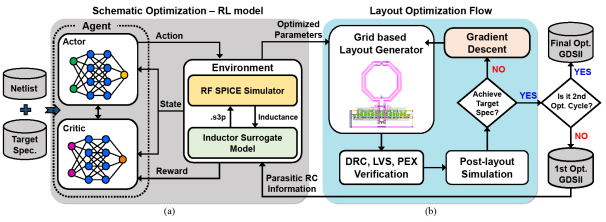

Diagram of the AI architecture (combining reinforcement learning and gradient-descent optimization) for automated LC‑VCO semiconductor design and layout; it visually explains how the model integrates schematic and physical layout steps to cut design time from months/weeks to about a day, directly illustrating the claim in the linked tweet.

Source: Financial News (image credited to UNIST / Ulsan National Institute of Science and Technology)

Research Brief

What our analysis found

한국 울산과학기술원(UNIST)과 경북대학교 공동 연구팀이 고성능 통신 반도체 회로 설계를 하루 만에 완료할 수 있는 AI 기술을 개발했다. 이 AI 모델은 5G·6G 고속 시스템에 핵심적인 LC 전압제어발진기(LC-VCO) 설계에 특화되어 있으며, 기존 자동화 방식으로 약 119시간 걸리던 작업을 28.5시간으로 단축해 설계 시간을 76% 이상 줄였다. 해당 연구는 2026년 4월 IEEE 저널 'Transactions on Computer-Aided Design of Integrated Circuits and Systems(TCAD)'에 온라인 게재됐다.

이 연구는 전 세계적으로 확산되는 AI 반도체 설계 트렌드의 일환이다. 구글 딥마인드의 알파칩(AlphaChip)은 강화학습과 그래프 신경망을 활용해 칩 플로어플래닝을 수개월에서 수시간으로 단축했으며, 2020년부터 구글 TPU 설계에 실제 적용되고 있다. 프린스턴대와 인도공과대(IIT) 연구팀 역시 무선 칩용 복잡한 전자기 구조 설계를 수주에서 수분으로 줄이는 AI를 개발했다. 현재 5nm 칩 설계 비용이 평균 5억 4,000만 달러에 달하고 864 엔지니어일(engineer days)이 소요되는 상황에서, AI는 비용과 개발 기간을 획기적으로 줄일 수 있는 핵심 기술로 주목받고 있다.

시놉시스(Synopsys)와 케이던스(Cadence) 같은 주요 EDA 업체들도 AI 기반 설계 자동화 도구를 적극 도입하고 있다. 시놉시스의 DSO.ai는 수배의 생산성 향상을 보고하고 있으며, 케이던스의 AI 도구는 1,000건 이상의 테이프아웃에 활용됐다. 그러나 전문가들은 AI가 여전히 설계 오류나 '환각(hallucination)' 문제를 일으킬 수 있어 인간 설계자의 감독이 필수적이며, 전체 칩 설계의 완전 자동화까지는 아직 갈 길이 남아있다고 지적한다.

Fact Check

Evidence from both sides

Supporting Evidence

UNIST·경북대 공동연구 직접 입증

2026년 5월 발표된 이 연구는 LC-VCO 회로 설계를 기존 119시간에서 28.5시간(약 하루)으로 76% 이상 단축했음을 실험으로 확인했으며, IEEE TCAD 저널에 게재되어 학술적 신뢰성을 확보했다.

구글 딥마인드 알파칩의 실전 적용

알파칩은 강화학습 기반으로 칩 플로어플래닝을 수개월에서 수시간으로 줄였고, 와이어 길이 약 6% 감소 및 에너지 소비 최대 67% 절감을 달성하며 2020년부터 구글 TPU에 실제 적용되고 있다.

프린스턴대·IIT 연구팀의 무선 칩 설계 AI

2025년 1월 발표된 연구에서 기존 수주가 걸리던 무선 칩용 전자기 구조 및 회로 설계를 수분 만에 완료하는 AI 기술이 개발되어, 다양한 반도체 영역에서 설계 시간 단축이 가능함을 보여준다.

주요 EDA 업체의 AI 도구 상용화

시놉시스의 DSO.ai는 아키텍처 탐색부터 배치·배선, 검증까지 자동화하며 수배의 생산성 향상과 2배 속도의 턴어라운드 타임을 보고하고 있고, 케이던스의 AI 도구는 1,000건 이상의 테이프아웃에 활용되어 산업 현장에서의 실효성이 검증되고 있다.

생성형 AI의 설계 주기 단축

2025년 이후 생성형 AI가 레이아웃 생성, 논리 합성, 검증 등에 적용되면서 개발 주기가 단축되고 있으며, AI 시스템은 24시간 작동이 가능해 품질 유지와 인적 오류 감소에 기여한다.

Contradicting Evidence

'하루 만에' 주장의 적용 범위 제한

UNIST 연구에서 입증된 '하루' 설계는 LC-VCO라는 특정 통신 회로에 한정된 결과이며, SoC(System on Chip) 전체나 수십억 트랜지스터 규모의 복잡한 프로세서 설계까지 하루 만에 가능하다는 의미는 아니다. 설계 대상의 복잡도에 따라 소요 시간은 크게 달라진다.

AI '환각' 문제와 인간 감독 필요성

AI 모델은 작동하지 않는 요소를 생성하거나 잘못된 배치를 제안하는 '환각(hallucination)' 현상을 일으킬 수 있어, 인간 설계자의 검증과 수정이 여전히 필수적이다. AI는 인간을 대체하기보다 생산성을 향상시키는 보조 도구로서의 역할이 강조된다.

데이터 부족과 학습 한계

효과적인 AI 모델 구축에는 대량의 고품질 데이터가 필요하지만, 반도체 설계 데이터의 독점적·기밀적 특성으로 인해 데이터 공유가 제한적이다. 또한 복잡한 AI 알고리즘의 개발과 훈련에는 상당한 컴퓨팅 자원과 전문 인력이 요구된다.

전체 설계 프로세스의 완전 자동화는 미완성

AI가 배치·배선, 최적화 등 많은 단계를 자동화하고 있지만, 아키텍처 설계부터 테이프아웃까지 전 과정의 완전 자동화는 아직 달성되지 않았으며, 전략적 판단과 혁신적 설계에는 인간의 개입이 계속 필요하다.

기존 EDA 도구와의 통합 과제

AI 기반 설계 도구를 기존 EDA 워크플로우에 원활히 통합하는 데는 데이터 포맷 차이, 호환성 문제, 조직 내 변화 저항 등의 현실적 장벽이 존재하며, 이는 산업 전반의 패러다임 전환 속도를 늦출 수 있는 요인이다.

Report an Issue

Found something wrong with this article? Let us know and we'll look into it.